Patent of the Month: Innovation Case Studies

Author: Jess Doocey | Published: March 14, 2026

Answer Capsule: What is the Patent of the Month?

The Swanson Reed Patent of the Month is an educational series that bridges the gap between complex engineering and tax law. Each month, our specialized technical teams analyze recently granted patents from across the United States. We break down the underlying technology and map its development process directly to the IRS Four-Part Test for Research and Development (R&D) Tax Credits. This provides corporate leaders, engineers, and CPAs with real-world case studies of what constitutes “qualified research.” Because we handle proprietary technical data in these assessments, our analyses adhere strictly to our internal Complaint and Privacy Policy, ensuring no confidential client trade secrets are ever disclosed.

Key Takeaways

- Real-World Application: We move beyond abstract tax theory to show exactly how specific software algorithms, manufacturing processes, and biotech formulas qualify for incentives.

- The Four-Part Test in Action: Every featured patent is analyzed through the lens of Permitted Purpose, Elimination of Uncertainty, Process of Experimentation, and Technological in Nature.

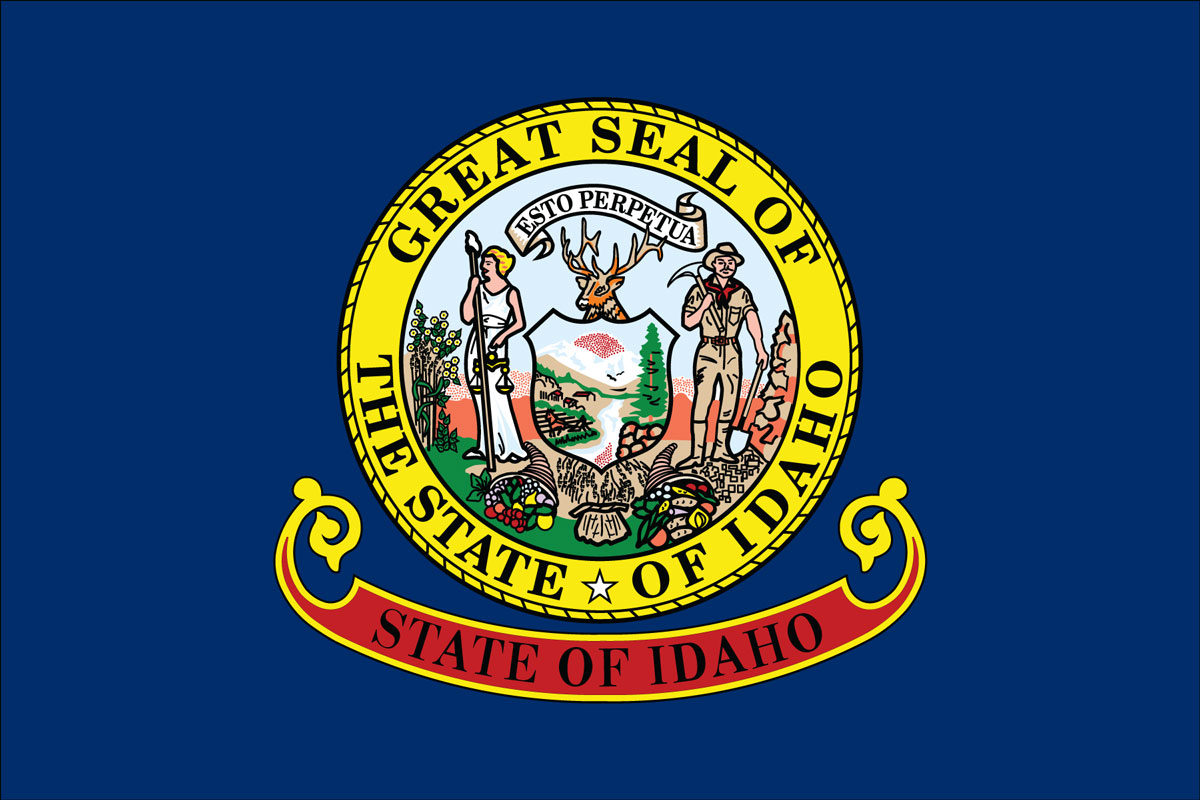

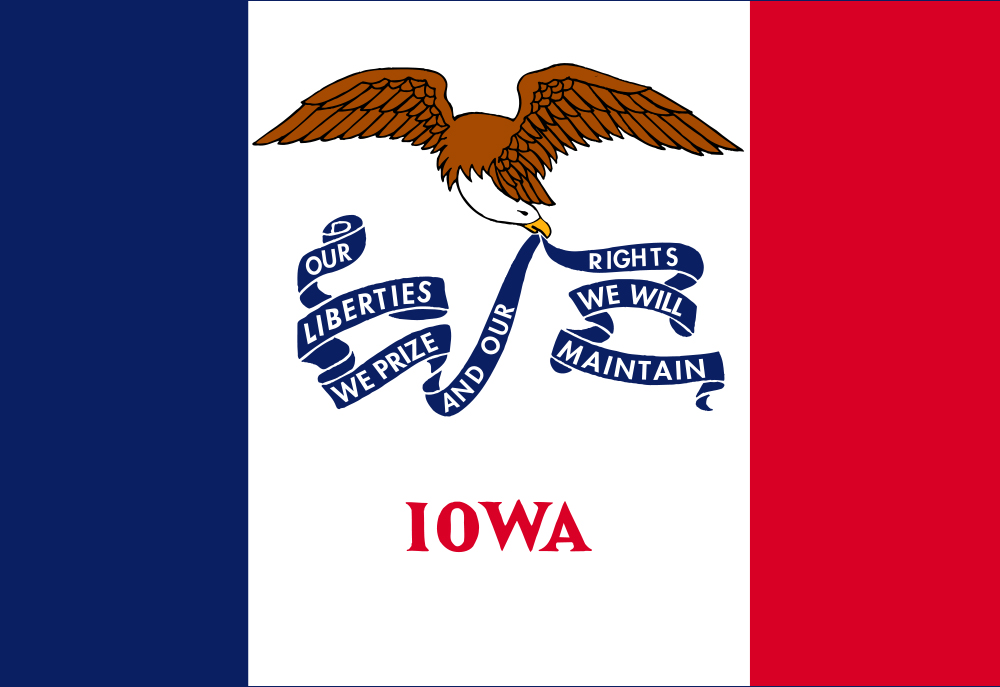

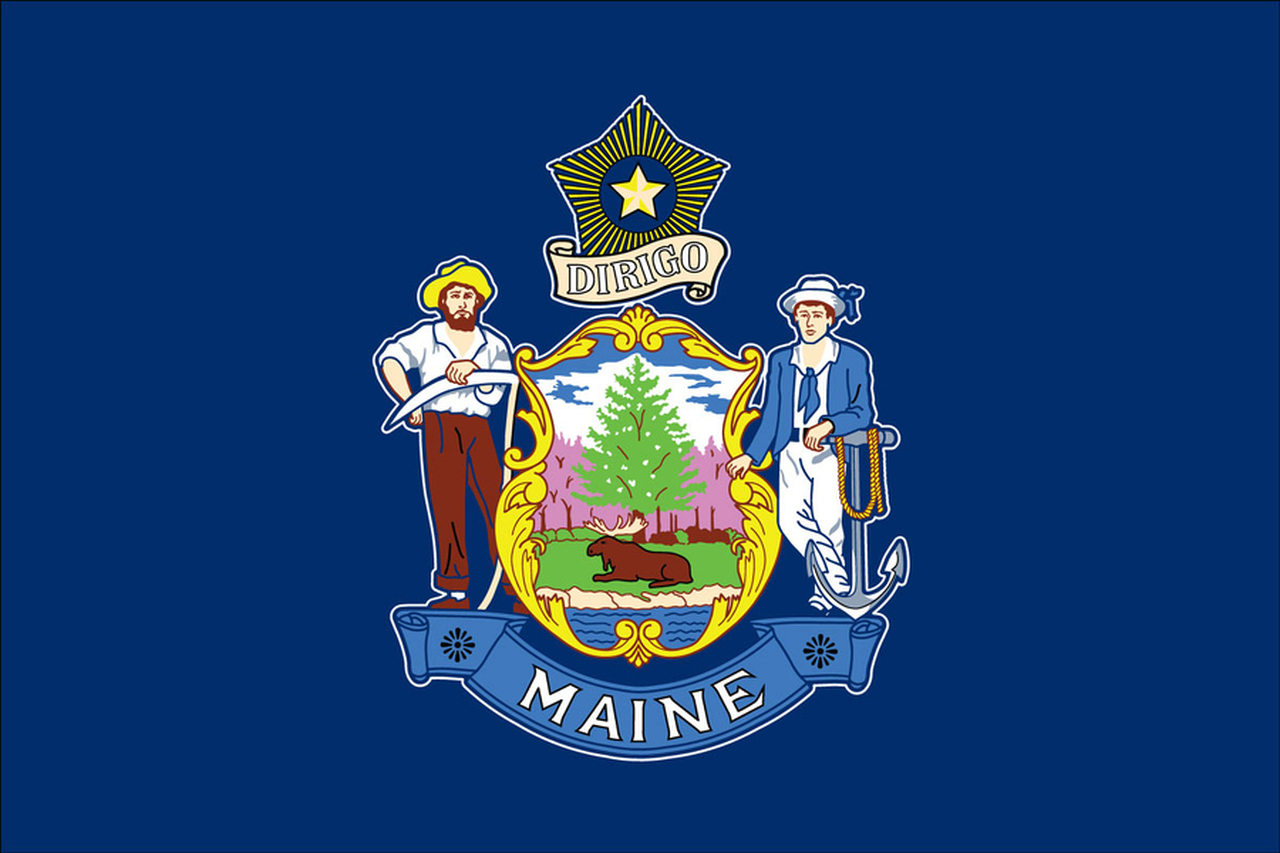

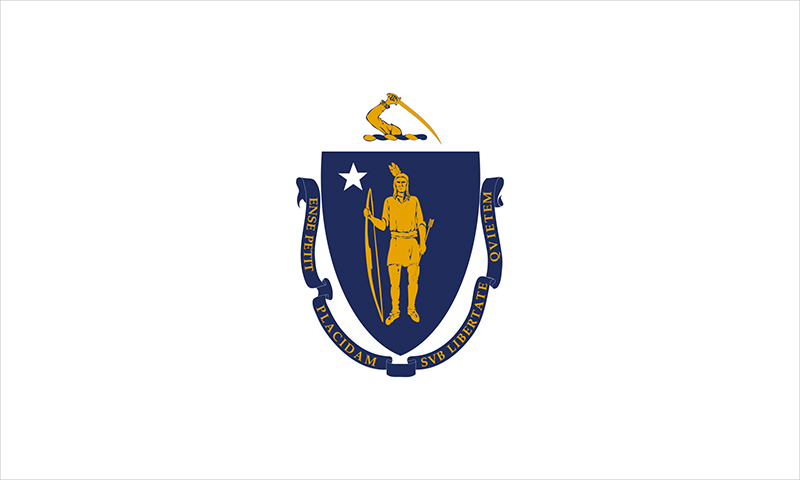

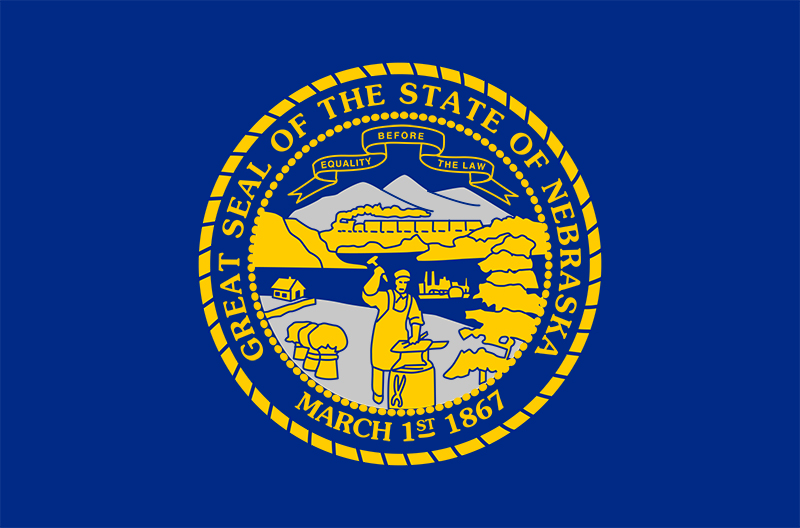

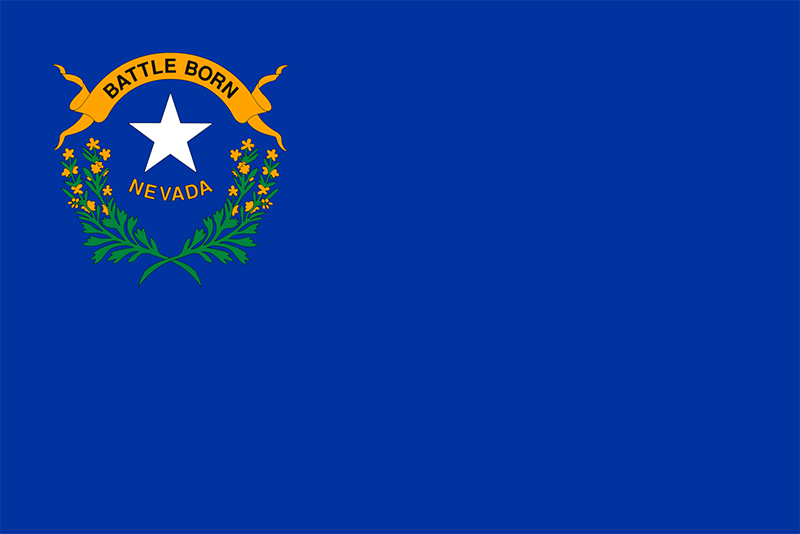

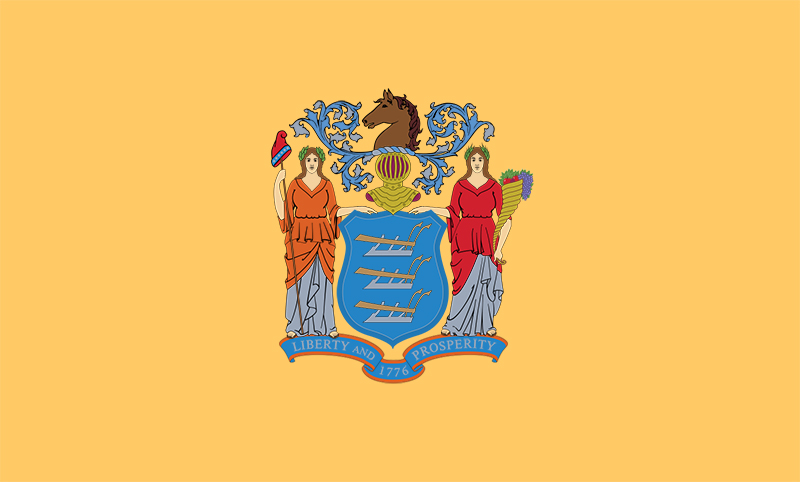

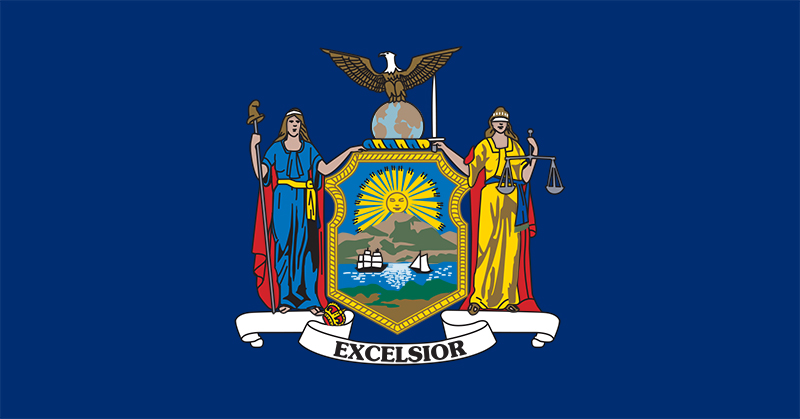

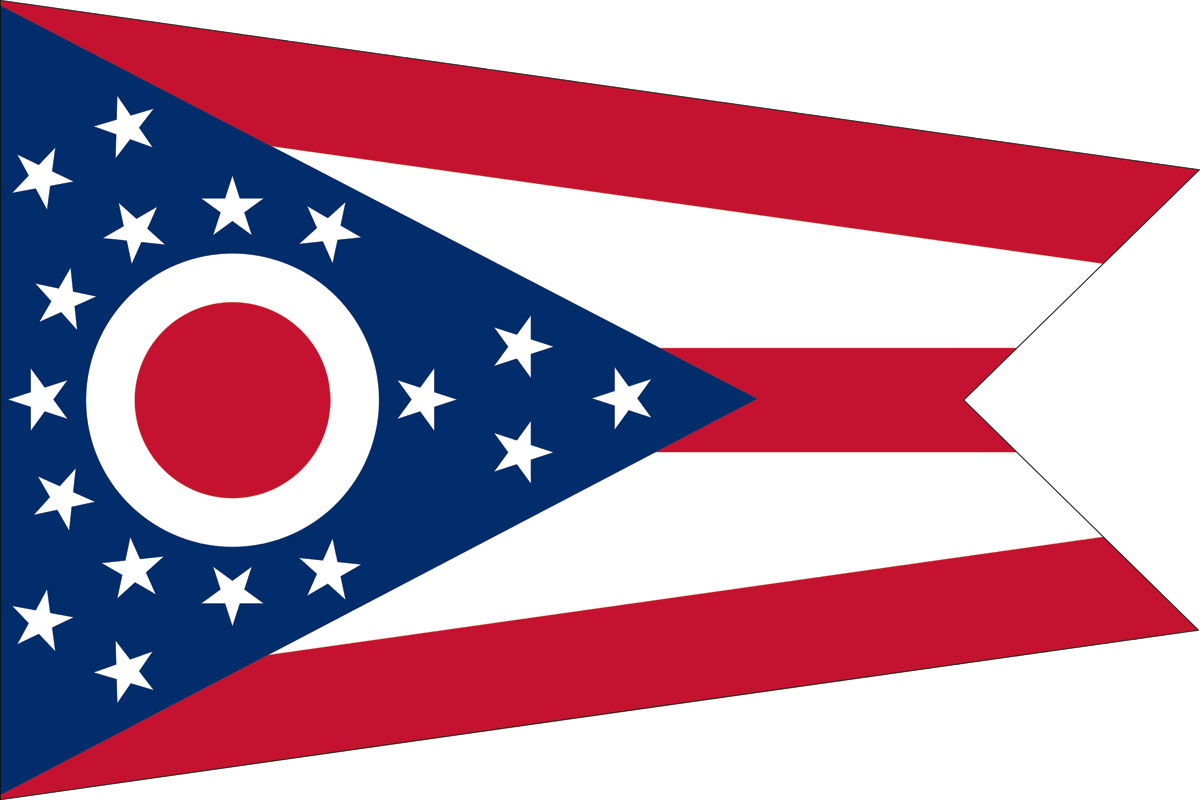

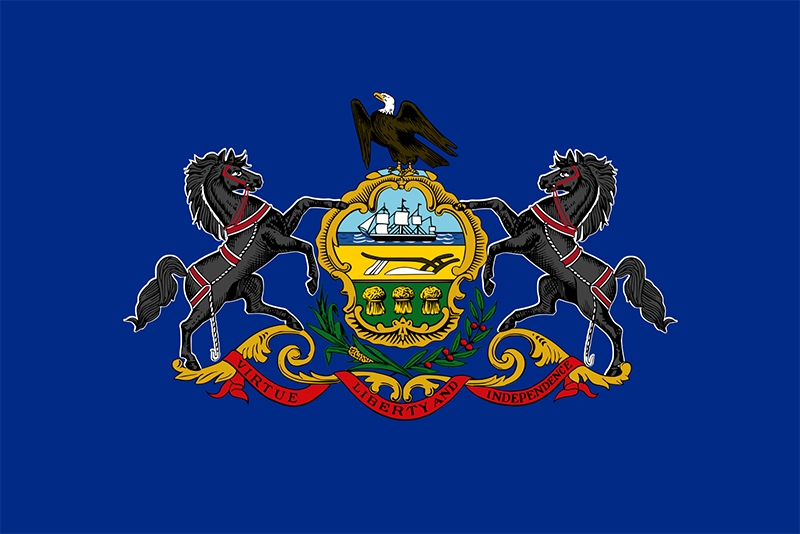

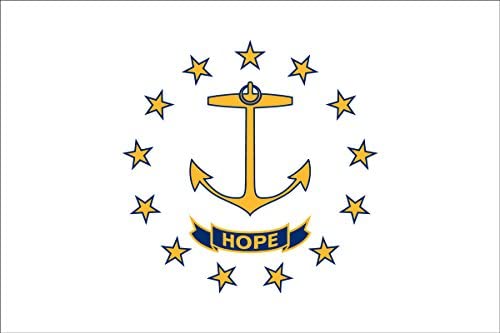

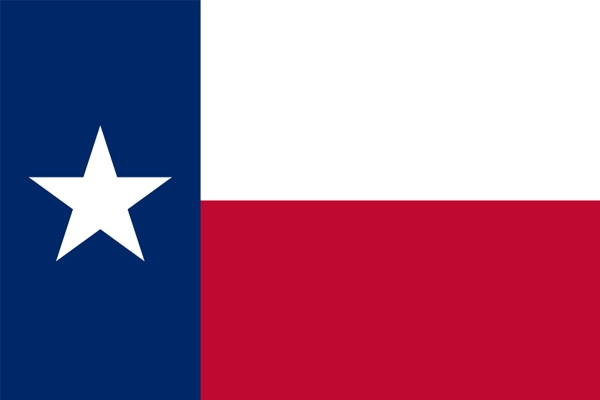

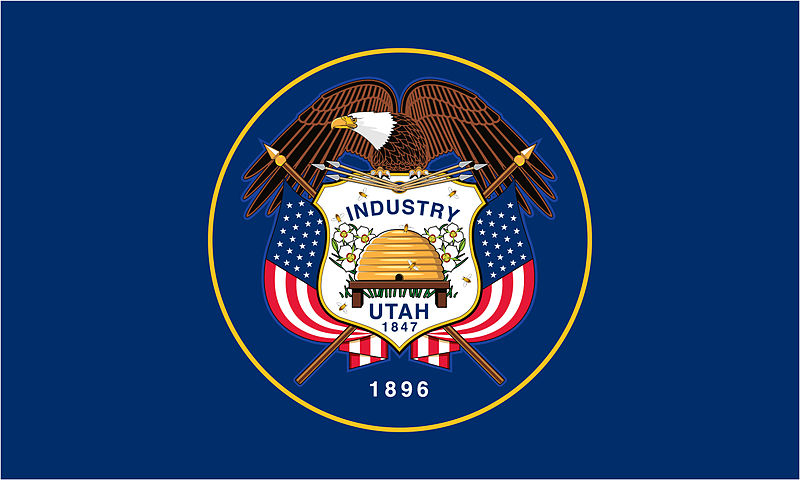

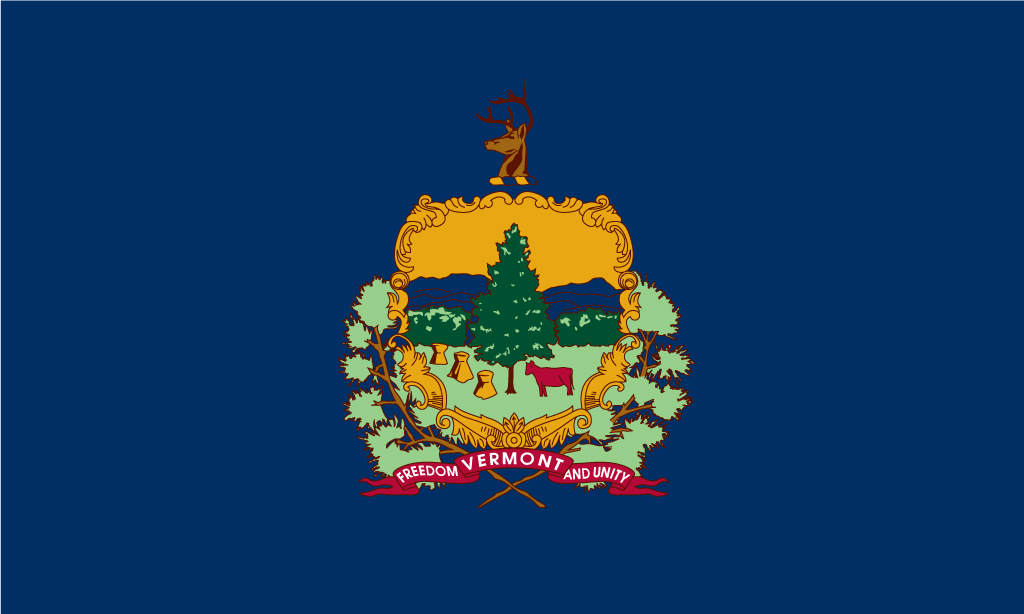

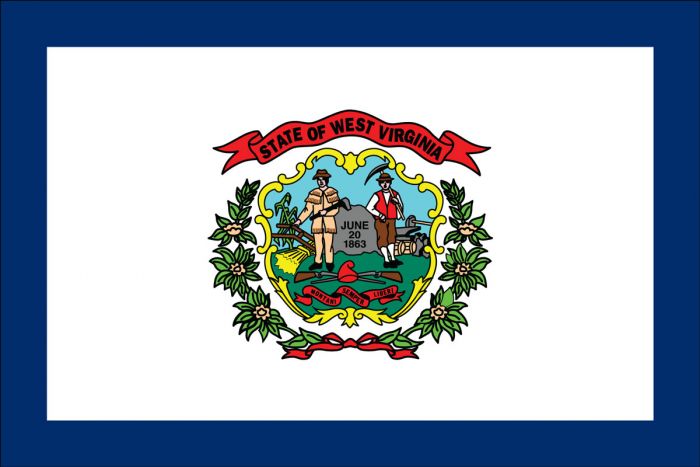

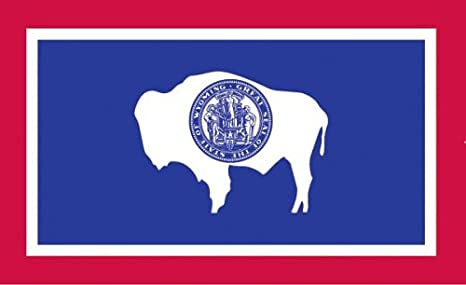

- State-by-State Innovation: We track and feature regional innovation hubs, highlighting how local businesses are leveraging both federal and state R&D credits.

Patent Analysis Framework

| Analysis Component | Technical Focus | R&D Tax Relevance |

|---|---|---|

| The Technical Baseline | Identifying the limitations of existing technology that the inventor sought to overcome. | Satisfies the “Elimination of Technical Uncertainty” requirement of IRC Section 41. |

| Iterative Development | Reviewing the prototypes, modeling, and testing phases required to finalize the patent. | Demonstrates the “Process of Experimentation” necessary for qualified research activities. |

| Industry Impact | How the invention improves performance, reliability, quality, or functionality. | Confirms the “Permitted Purpose” rule required for tax credit eligibility. |